SPEF 란?

SPEF는 설계(R, L, C)의 기생 정보를 ASCII( American Standard Code for Information Interchange exchange format)로 표현할 수 있도록 합니다. 사용자는 SPEF 파일의 값을 읽고 확인할 수 있습니다. 사용자는 이 파일을 수동으로 생성하지 않으며 도구에 의해 자동으로 생성됩니다. 주로 한 도구에서 다른 도구로 기생 정보를 전달하는 데 사용됩니다.

상호 연결 기생은 프로세스에 따라 다릅니다. SPEF는 최상의 경우, 일반 및 최악의 경우 값과 같은 모든 경우의 사양을 지원합니다. 이러한 삼중항(최상, 일반 및 최악)은 R, L 및 C 값, 포트 속도 저하 및 로드에 대해 허용됩니다. 기생 R, C 및 인덕턴스 L의 단위는 SPEF 파일의 시작 부분에 지정됩니다.

SPEF가 P&R 또는 PEX에 의해 생성할 수 있으며, 이렇게 생성된 SPEF file은 타이밍을 확인하기 위한 Timing Signoff tool, Circuit simulation, Crosstalk Analysis을 수행하는 데 사용됩니다.

Parasitics 성분은 다양한 수준에서 표현될 수 있습니다. SPEF는 세 가지 모델을 지원합니다.

Distributed net model

이 모델(D_NET)에서 네트 루트의 각 세그먼트에는 고유한 R 및 C 값이 있습니다.

Reduced net model

이 모델(R_NET)에서는 net의 load pin에 하나의 reduce R과 C가 있고 net의 driver pin에 pie model(CRC)이 고려된다.

Lumped capacitance mode

이 모델에서는 전체 네트에 대해 단일 커패시턴스만 지정됩니다.

SPEF는 세부 기생의 압축 형식입니다. 디자인을 위한 SPEF 파일은 여러 파일로 분할될 수 있으며 계층적일 수도 있습니다. SPEF는 간결함과 완전성으로 인해 설계에서 기생을 표현하기 위해 선택하는 형식입니다.

두 개의 팬아웃(*I *8 및 *I *10)이 있는 net의 example

*D_NET NET_27 0.77181

*CONN

*I *8: Q O *L 0 *D CELL1

*I *10: I I*L 12.3

*CAP

1 *9:0 0.00372945

2 *9:1 0.0206066

3 *9:2 0.035503

4 *9:3 0.0186259

5 *9:4 0.0117878

6 *9:5 0.0189788

7 *9:6 0.0194256

8 *9:7 0.0122347

9 *9:8 0.00972101

10 *9:9 0.298681

11 *9:10 0.305738

12 *9:11 0.0167775

*RES

1 *9:0 *9:1 0.0327394

2 *9:1 *9:2 0.116926

3 *9:2 *9:3 0.119265

4 *9:4 *9:5 0.0122066

5 *9:5 *9:6 0.0122066

6 *9:6 *9:7 0.0122066

7 *9:8 *9:9 0.142205

8 *9:9 *9:10 3.85904

9 *9:10 *9:11 0.142205

10 *9:12 *9:2 1.33151

11 *9:13 *9:6 1.33151

12 *9:1 *9:9 1.33151

13 *9:5 *9:10 1.33151

14 *9:12 *8: Q 0

15 *9:13 *10: I 0

*END

SPEF 파일의 내용 :

header_definition: SPEF 버전 번호, 디자인 이름 및 R, L 및 C 단위와 같은 기본 정보를 포함합니다.

[name_map]: 인덱스에 대한 네트 이름 및 인스턴스 이름의 매핑을 지정합니다.

[power_definition]: 전력망 및 접지망 선언

[external_definition]: 디자인의 포트를 정의합니다.

[define_definition]: SPEF가 추가 파일에 설명된 인스턴스를 식별합니다.

internal_definition: 디자인의 기생인 파일의 내장을 포함합니다.

헤더 정의

*SPEF "IEEE 1481-1999" ------------> SPEF 버전

* DESIGN "ddrphy1" ------------------> 디자인명

* DATE "Fri Sep 21 00:49:32 2005" ---> 파일이 생성된 타임스탬프

* VENDOR "SGP Design Automation_1" ---> 공급업체 도구

* VERSION "V2000.09" ----> SPEF를 생성하는 데 사용된 프로그램의 버전 번호

* DESIGN_FLOW "PIN_CAP NONE" "NAME_SCOPE LOCAL" ---> SPEF 파일이 생성된 단계를 지정합니다. 파일을 읽어서 파생할 수 없는 SPEF 파일에 대한 정보를 설명합니다.

* DIVIDER / -----> 는 계층 구분자를 지정합니다.

* DELIMITER: --> 핀과 해당 인스턴스 사이의 구분 기호입니다.

* BUS_DELIMITER [ ] ---> 버스의 비트를 식별하는 데 사용되는 접두사와 접미사를 지정합니다.

* T_UNIT 1.00000 NS ---> NS | PS: 시간 단위를 지정합니다.

* C_UNIT 1.00000 FF ----> PF | FF: 커패시턴스 단위를 지정합니다.

* R_UNIT 1.00000 OHM -----> OHM | KOHM: 저항 단위를 지정합니다.

* L_UNIT 1.00000 HENRY -----> HENRY | MH | UH: 인덕턴스 단위를 지정합니다.

SPEF file 에서 주석은 아래 두가지 케이스가 가능함.

// Comment - until end of line.

/* This comment can be extended to multiple lines */

NAME MAP:

인덱스에 대한 net 이름 및 instance 이름의 맵으로 구성된 name map은 SPEF 파일 크기가 효과적으로 작아지고, 모든 긴 이름이 한 곳에만 표시됩니다. 고유한 정수 값(인덱스)에 대한 이름 매핑을 지정합니다.

Format of Name Map:

*NAME_MAP

*positive_integer name

*positive_integer name

. . .

Example of Name Map

*NAME_MAP

*1 memclk

*2 memclk_2x

*3 reset_

*4 refresh

*5 resync

*6 int_d_out[63]

*7 int_d_out[62]

*8 int_d_out[61]

*9 int_d_out[60]

*10 int_d_out[59]

*11 int_d_out[58]

*12 int_d_out[57]

. . .

*364 mcdll_write_data/write19/d_out_2x_reg_19

*366 mcdll_write_data/write20/d_out_2x_reg_20

*368 mcdll_write_data/write21/d_out_2x_reg_21

. . .

*14954 test_se_15_S0

*14955 wr_sdly_course_enc[0]_L0

*14956 wr_sdly_course_enc[0]_L0_1

*14957 wr_sdly_course_enc[0]_S0

이것은 미리 이름의 reference를 만들어줌으로써 파일 사이즈를 줄이는 데 도움을 주고, 이름은 instance 또는 net 이름이 들어가야한다.

따라서, name map은 긴 이름과 path가 반복되는 것을 막는다, 그들의 고유 번호를 사용함으로써,

POWER DEFINITION SECTION:

Defines the power and ground nets.

*POWER_NETS VDDQ

*GROUND_NETS VSSQ

EXTERNAL DEFINITION SECTION:

이것은 physical & logical ports of the design 을 포함한다.

Logical ports Format:

*PORTS

port_name direction {conn_attribute}

. . .

Example:

*PORTS

*1 I

*2 I

*3 I

*4 I

*5 I

*6 I

*7 I

*8 I

*9 I

*10 I

*11 I

. . .

*450 O

*451 O

*452 O

*453 O

*454 O

*455 O

*456 O

여기서 I는 입력, O는 출력, B는 양방향입니다.

PHYSICAL PORTS

Format:

*PHYSICAL_PORTS

pport_name direction {conn_attribute}

DEFINE DEFINITION SECTION:

현재 SPEF에서 참조되는 엔터티 인스턴스를 정의합니다.

*DEFINE instance_name {instance_name} entity_name

*PDEFINE 물리적 인스턴스 엔티티_이름

*PDEFINE ---> 엔티티 인스턴스가 논리적 파티션이 아닌 물리적 파티션인 경우에 사용됩니다.

예시:

*DEFINE 코어/u1ddrphy 코어/u2ddrphy "ddrphy1"

이는 *DESIGN 값이 ddrphy1인 다른 SPEF 파일이 있음을 의미합니다. 이 파일에는 ddrphy1 디자인에 대한 기생 요소가 포함되며 물리적 및 논리적 계층 구조를 가질 수 있습니다.

INTERNAL DEFINITION SECTION:

설계에서 그물에 대한 기생을 설명합니다. 기본적으로 두 가지 형식이 있습니다.

- Distributed net, D_NET

- Reduced net, R_NET

net *5426(D_NET)에 대한 분산 네트 기생의 예.

*D_NET *5426 0.899466

*CONN

*I *14212: D I *C 21.7150 79.2300

*I *14214: Q O *C21.495076.6000*DDFFQX1

*CAP 1

*5426:10278 *5290:8775 0.217446

2 *5426:10278 *16:3754 0.0105401

3 *5426:10278 *5266:9481 0.0278254

4 *5426:10278 *5116:9922 0.113918

5 *5426:10278 0.529736

*RES

1 *5426:10278 *14212: D 0.340000

2 *5426:10278 *5426:10142 0.916273

3 *5426:10142 *14214: Q 0.340000 *END

첫 번째 줄에서 * D_NET *5426 0.899466: *5426 은 순 지수이고 0.899466은 순의 총 정전 용량 값입니다.

커패시턴스 값은 접지된 것으로 가정되는 교차 결합 커패시턴스와 부하 커패시턴스와 같은 네트의 모든 커패시턴스의 합입니다.

*DESIGN_FLOW 정의에서 PIN_CAP 설정에 따라 핀 커패시턴스를 포함하거나 포함하지 않을 수 있습니다.

두 번째 줄에는 네트의 드라이버와 로드를 설명하는 연결 섹션이 있습니다. 입력:

*CONN

*I *14212: D I *C 21.7150 79.2300

*I *14214: Q O *C 21.4950 76.6000 *D DFFQX2

여기서

*I-----> internal pin

*14212: D --> instance of D pin.

*14212--> index number

I -------> load (input pin) on the net.

O ------> Driver (output pin) on the net.

*C -----> coordinates of the pin

*D-----> driving cell of the pin.

CAPACITANCE SECTION:

이 섹션에서는 분산 네트의 커패시턴스를 설명합니다

1 *5426:10278 *5290:8775 0.217446

2 *5426:10278 *16:3754 0.0105401

3 *5426:10278 *5266:9481 0.0278254

4 *5426:10278 *5116:9922 0.113918

5 *5426:10278 0.529736

첫 번째 숫자는 정전 용량 식별자입니다. SPEF에는 두 가지 형태의 커패시턴스 사양이 있습니다.

첫 번째 ~ 네 번째는 à (첫 번째 ~ 네 번째) 형식입니다. 두 네트 사이의 교차 결합 커패시턴스를 지정합니다. 따라서 인덱스 1에서 커패시턴스는 0.217446이고 네트 *5426과 *5290 사이의 교차 결합 커패시턴스를 나타냅니다.

다섯 번째는 인덱스 5)가 있는 두 번째 형식입니다. 접지에 대한 커패시턴스를 지정하고 커패시턴스 인덱스 5에서 접지에 대한 커패시턴스는 0.529736입니다 .

첫 번째 노드 이름은 반드시 D_NET의 네트 이름이어야 하며 여기서 D_NET의 이름은 *5426입니다. *5426:10278의 양의 정수 10278은 내부 노드 또는 접합점을 지정합니다.

따라서 커패시턴스 지수 4는 내부 노드 10278이 있는 net *5426과 내부 노드 9922가 있는 net *5116 사이에 결합 커패시턴스가 있으며 이 결합 커패시턴스의 값은 0.113918임을 나타냅니다.

RESISTANCE SECTION

분산 네트의 저항을 설명합니다.

*RES

1 *5426:10278 *14212: D 0.340000

2 *5426:10278 *5426:10142 0.916273

3 *5426:10142 *14214: Q 0.340000

첫 번째 필드는 저항 식별자입니다.

첫 번째 인덱스는 내부 노드 *5426:10278에서 *14212의 D 핀 사이에 있으며 저항 값은 0.34입니다.

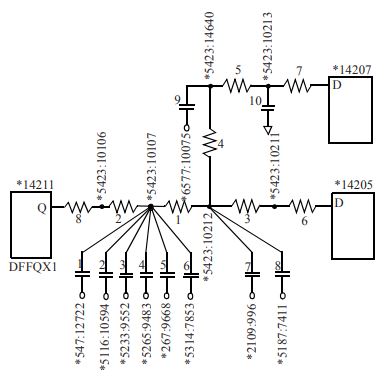

커패시턴스 및 저항 섹션은 아래 그림으로 표시된 RC 네트워크로 더 잘 이해할 수 있습니다.

분산 네트의 두 번째 예:

이 네트에는 2개의 부하와 1개의 드라이버가 있으며 네트의 총 커패시턴스는 2.69358입니다.

*D_NET*5423 2.69358

*CONN

*I *14207: D I *C 21.7450 94.3150 ------> load

*I *14205: D I *C 21.7450 90.4900------>load

*I *14211: Q O *C 21.4900 83.8800 *D DFFQX1-----------> driver

*CAP

1 *5423:10107 *547:12722 0.202686

2 *5423:10107 *5116:10594 0.104195

3 *5423:10107 *5233:9552 0.208867

4 *5423:10107 *5265:9483 0.0225810

5 *5423:10107 *267:9668 0.0443454

6 *5423:10107 *5314:7853 0.120589

7 *5423:10212 *2109:996 0.0293744

8 *5423:10212 *5187:7411 0.526945

9 *5423:14640 *6577:10075 0.126929

10 *5423:10213 1.30707

*RES

1 *5423:10107 *5423:10212 2.07195

2 *5423:10107 *5423:10106 0.340000

3 *5423:10212 *5423:10211 0.340000

4 *5423:10212 *5423:14640 1.17257

5 *5423:14640 *5423:10213 0.340000

6 *5423:10213 *14207: D 0.0806953

7 *5423:10211 *14205: D 0.210835

8 *5423:10106 *14211: Q 0.0932139

*END

Figure RC network for D_NET *5423 corresponds to the distributed net specification.

일반적으로 내부 정의는 다음 사양으로 구성될 수 있습니다.

D_NET: 논리적 네트워크의 분산 RC 네트워크 형태

R_NET: 논리적 네트워크의 축소된 RC 네트워크 형태

D_PNET: 물리적 네트의 분산 형태

R_PNET: 물리적 네트의 축소된 형태

*R_NET net_index total_cap [*V 라우팅_신뢰] [드라이버_감소]

*D_PNET pnet_index total_cap [*V 라우팅_신뢰] [pconn_section] [pcap_section] [pres_section] [pinduc_section]

*END

*R_PNET pnet_index total_cap [*V 라우팅_신뢰] [pdriver_reduction]

*END

다음은 구문입니다.

*D_NET net_index total_cap [*V 라우팅_신뢰]

[연결 섹션]

[캡_섹션]

[res_section]

[인덕턴스_섹션]

*END

인덕턴스 섹션

인덕턴스와 형식을 정의하는 데 사용되는 이 섹션은 저항 섹션과 매우 유사합니다.

*V는 네트의 기생 정확도를 지정하는 데 사용됩니다. 정확도는 다음과 같이 ROUTING_CONFIDENCE 값과 함께 *DESIGN_FLOW 문을 사용하여 net 및 전역적으로 개별적으로 지정할 수 있습니다.

*DESIGN_FLOW "ROUTING_CONFIDENCE 100" ---> 최종 셀 배치 및 최종 경로 및 3d 추출이 사용된 후 기생체가 추출되었음을 의미합니다.

라우팅 신뢰도의 가능한 값은 10, 20, 30, 40, 50, 60, 70, 80, 90 및, 100입니다.

감소된 순

분산 네트에서 감소된 네트입니다. 네트에는 각 드라이버에 대해 하나의 드라이버 감소 섹션이 있습니다. 감소된 순 SPEF의 예는 다음과 같습니다.

*R_NET *1200 2.995

*드라이버 *1201: Q ----> 드라이버 핀 _이름

*셀 SEDFFX1

*C2_R1_C1 0.511 2.922 0.106 ----> 네트의 드라이버 핀에 있는 파이 모델의 기생을 보여줍니다.

*로드 *RC *1202: A 1.135

*RC *1203: A 0.946 --------> *RC 구성의 rc_value는 Elmore 지연(R*C)입니다.

*END

그리고 RC 네트워크의 그림은 아래와 같습니다.

LUMPED CAPACITANCE MODEL:

총 커패시턴스만 있고 다른 정보는 제공되지 않는 *D_NET 또는 *R_NET 구성을 사용하여 정의할 수 있습니다. 집중 커패시턴스의 예는 다음과 같습니다.

*D_NET *1 80.2096

*CONN

*I *2: YO *L 0 *D CLKMX2X3

*P *1 O *L 0 *END

*R_NET *17 58.5204

*END

SPEF 파일의 값은 0.243: 0.269: 0.300과 같이 프로세스 변동을 나타내는 삼중항 형식일 수 있습니다.

0.243 ----> 최상의 경우 값

0.269 ----> 일반 값

0.300----> 최악의 경우 값.

'VLSI > VLSI기초' 카테고리의 다른 글

| lsf(Load Sharing Facility) (0) | 2020.08.11 |

|---|---|

| [VLSI기초 - CMOS logic] 3. Modeling of CMOS Cells (0) | 2020.05.25 |

| [VLSI기초 - CMOS logic] 2. Cell - Standard Cell (0) | 2020.05.25 |

| [VLSI기초 - CMOS logic] 1. CMOS logic basic (0) | 2020.05.25 |

| [VLSI기초 - CMOS logic] 0. MOSFET(NMOS, PMOS) (0) | 2020.05.25 |

댓글